どらびです.

本記事はシリーズものの5つ目の記事になりますので,以前のをご覧になっていない方はそちらもご参照頂ければと思います.

ということで,今回は自作基板の失敗後,再構築中の構成について書いていこうと思います.

構成の再考

メインチップの再選定

前回の記事で「メインチップは変えたくない」と言ったな,あれはウソだ.(ウソではない)

というわけで,前回の失敗から3年ほど経過しているわけですが,そもそも構想し始めたのも大分前なのでzynq(MPじゃない)は今のFPGA SoCのラインナップから見ると貧弱な構成なのではないかと感じていたこともあり,変更することにしました.

というか気になるのが出てきたからなんですけどね.これです.

なんでコイツが気になったのかというとまずはスペック面.

RISC-Vの勉強にもなるし,64bitクアッドコアで性能も上がっており,何よりDDR4に対応しているのが個人的に乗り換えのきっかけになっています.

次に,安い評価ボードが出回っていた点.

(早速購入しました.)

正直これに乗り換えようと決意して色々調べた後で気づいた話なので後付けですが,上記評価ボードはオープンソースなので回路図がすべて公開されています.しかもスキャナカメラに搭載したいペリフェラルがこのボードに概ね揃っているので,コイツの回路図をほぼ丸パクリした上で不要なものを削ってサイズを調整することで,失敗のリスクを低減しながら自作SoC基板を作成できると踏んだわけです.(失敗からだいぶ学習した)

前回選定していたzynqと比べて円安なのもあって値段が高めですが,10個買うと単価でzynq(を一個買う時の価格)を下回るくらいの値段で,84ピン増えた上に公式で割と簡単にMIPI-DSIを扱えると記述されているので(私のプログラミングスキル次第では)以前搭載予定だった画像処理用の小さなFPGAなしで済む分,トータルでは安上がり&スペース節約ができそうな見込みです.

全体構成の見直し

というわけでメインチップ変更したので,構成はほぼ全て変更になるレベルです.

ついでに,前回の反省をさらに?活かしてもうひとつ大幅に変更しようと考えています.

それは「電源管理を別基板に起こす」という点です.

これは純粋に前述したように,評価ボード丸パクリな回路構成を作る上で電源部分を新規に起こすのがリスクになるからです.また,筐体デザインの現在の状態的に,うまいことやればむしろ基板を分けた方がスペース的には都合が良くなりそうな見込みでいます.

それに伴って充電用と通信用のUSBコネクタを分けようかなとかも考えています.

全てはサイズに収まるか否か次第なので,この辺はまだちょっと変更の余地がある部分ですね…

評価ボードでのユニットテスト

いきなり基板設計してもうまくいかないというのは11万円の散財で嫌というほど思い知ったので,「急がば回れ」の精神で評価ボード上でやりたいことができるのか検証してみています.

なお,ここから先FPGAの詳しい設定等に関しては現在のところオープンソースで行くか未定なのでぼかしておきたいというのと,いずれにしても備忘録的に手順はある程度ブログ内でまとめようと思っているものの,ここにまとめるには情報量が多くなりすぎてしまうので,ここでは大雑把な内容の説明にとどめておきます.(個別記事書いたら随時ここにリンク置く形で行きます.)

センサ基板動確

まずはLVDSでセンサ基板から正しくデータを取ってこれるかになります.これができないと話が始まりません.

しかも,前回の記事でも書いた通り,まだセンサ基板自体動確がすべてできているわけではないので,こちらのデバッグも兼ねての検証になります.

MIPI-DSI

こちらも必須,エンベデッドなモニタへのアウトプット手段としては結構一般的だと思われるMIPI-DSIの出力も対応しているので当然検証したいところなのですが,非常に残念なことに評価ボードの電圧設定の兼ね合いで,この評価ボード(BeagleV-Fire)を使う限りMIPI-DSIのテストは不可能となっています.なのでここは致し方ないですが本番基板で一発動確せざるを得ないポイントになっています.

M.2(×2)

次にM.2.今回の評価ボード,元からM.2スロットが付いています.

M.2自体パソコンを触る人じゃないと知らないかもしれませんが,要は基板拡張用のスロットの一種です.

で,M.2といっても切り欠きの位置で種類がいくつかありまして,評価ボードにはE-keyというのが付いています.これはよくwifiの機能を追加するためのカードによく使われるものです.

実際に評価ボードにwifiの機能追加ができるかどうかに関しては既に試しており,実際に使えました.

でここからが本題なのですが,この評価ボードはフル機能使っているわけではなくかなり機能をセーブしています.簡単に言うとM.2スロットをもう一個足せるので,SSDをさせるようにしておこうと思います.大容量のSSDを指しておけばSDとかCFexpressカードよりも容量あたりの単価を抑えつつ,読み書きも高速なストレージを用意できるので,結構な強みになるんじゃないかと思っています.

【補足】BeagleV-FireのM.2スロット周りの仕様について

上記で軽く述べている通り,BeagleV-FireはM.2周りの仕様に関してセーブ?している状態です.備忘録も兼ねてその辺は少し詳しめにも書いておきます.興味ない人はスルーでOKです.

まず,M.2スロットの中身ですが,実質PCIexpressです.グラボとか挿すのに使われているやつですね.

で,BeagleV-fireに積まれているMicrochipのPolarfire SoCシリーズにおけるPCIexpressの機能なのですが,FPGA部で独自実装するのは(できるかどうかすらわかっていませんが)別として,標準的には?XCVRと呼ばれるトランシーバ専用のバンクに4ペア(1ペアで受信送信それぞれ差動なので計4本ある.)が割り当てられています.

グラボとかによく記載されていますが,PCIexpressはこの1ペアをレーンと呼び,PCIe×16などのように「×~~」のように表現します.

要はBeagleV-fireでは4レーンまで用意できる訳ですね.

レーンは2の階乗の組み合わせしかないので,実際にBeagleV-fireで使用できる可能性があるのは×1,×2,×4のいずれかになります.

これがまずレーンについての説明です.

次に,例えばですが×2レーンのPCIeスロットを2つ作る,というようにレーンを分割して複数のスロットを作ることもできます.

ただし,スロットは2つまでしか作れない仕様になってます.(ユーザガイド見てますが物理的な理由はよくわからなかったので仕様という事で.)

という事で,例えばですが,×1のスロットと×2のスロットを一個ずつとかはできます.

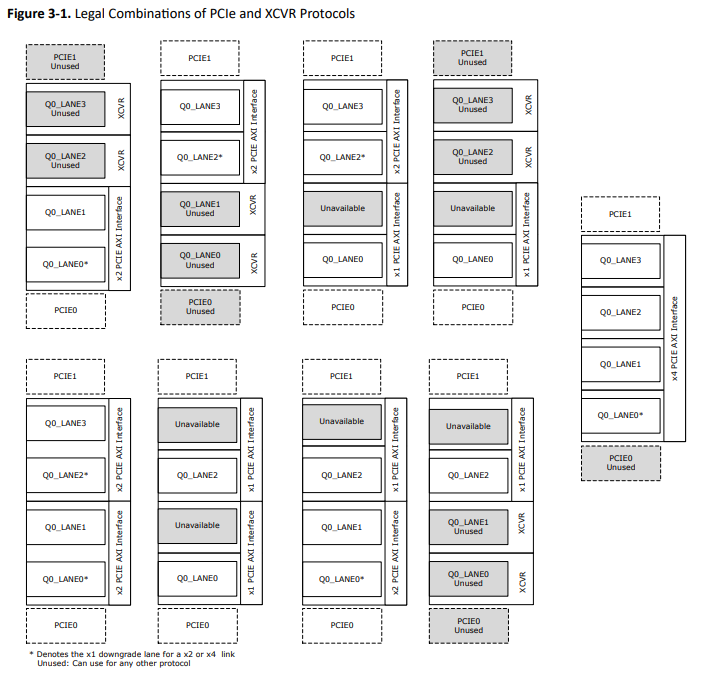

詳細はユーザガイドから引用しました下図を見てみてください.実現可能なPCIeおよびXCVR(他の任意のトランシーバプロトコルをアサインできる)の組み合わせが記載されています.

自分の場合,XCVRじゃない通常のGPIOでもLVDSの受信とMIPI-DSIは共存できるのでbank1のVDDIを2.5Vに設定すれば大体のやりたいことは出来そうという事で,上図で言うところの左下,×2レーン2つにする方針です.

まとめ

今このFPGA SoCで絶賛お勉強&テスト中ですので,各項目に関する詳細は備忘録も兼ねて細々と交信していこうと思っています.まずは進捗出さないとですね…

FPGAの何が嫌かと聞かれたら学習コストが高すぎるの点に尽きる気がするので,次回更新がいつになるかはわかりません.まあ以前から不定期にもほどがあるというレベルなので,(読んでいる人がいればですが)気長にお待ちいただければと思います.

それではー.

コメント