ちょっと期間が空いてしまいました.相変わらず3歩進んで2歩どころか3歩くらい下がったりしているので同じようなところをうろついております.

が,なんで同じところうろついてたのか記録しないと,手戻りした時にまた同じ過ちを犯すんですよね…

うっすら記憶していて回避しようとしても,何をどうミスったか調べるのに結局時間を食うというところで,メモは非常に重要です.ここはもうそういう場だと思っているので忘れる前に書いていきます.

- 概要編

- 仕様決定編

- 回路設計編

- 機構設計編

- 初期試作&大爆死編

- 試作第二弾

- polarfire編①

- polarfire編②

- polarfire編③

- polarfire編④

前回はlinuxを思い通りの設定でビルドでき,ようやくADCからのデータ読み出しができるのでは??

という激アツ展開でした.

次はいよいよ

- linuxからCCDコントローラを設定し

- UIOでDMAコントローラを設定し

- CCDセンサからのデータをDMAでFPGAからMSS(マイコン)のDDRに送り

- DDRの値を確認して画像が取得できているかを確認する

というのを順を追って確認していきます.

CCDからのデータ読み出し

はい.というわけでデータを読み出しましょう…とはならないのが定番の展開です.

linuxからADCを駆動し,DMAやuioを設定して読み出しを始めるためのスクリプトは以前からざっくり作り上げていたので動作させてみましたが,データが流れてくる気配がありません.

(※スクリプトは今のところ公開する予定はないですが,必要に応じて公開するかもしれません.今は詳細は控えておきます.念のため.)

どこが悪くてデータのやり取りができてないのか確定しているわけではないのですが,とりあえず色々ミスも見つかったりで手直ししているうちに一つ重大なミスに気づきました.

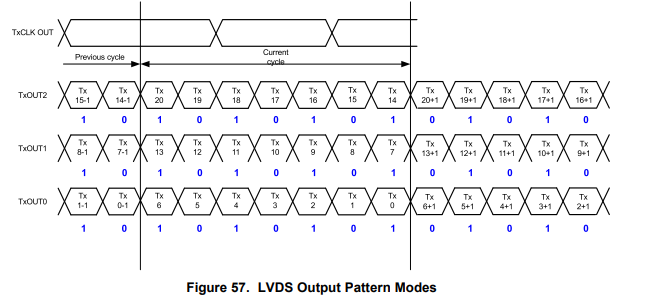

下図はCCDコントローラ(要はADC)から出てくるデータのフォーマットです.

LVDSのクロックはデータ7bitに対してrise→fall→riseする,microchipのデータシートでの表現を借りると「fractional aligned」なデータでした.

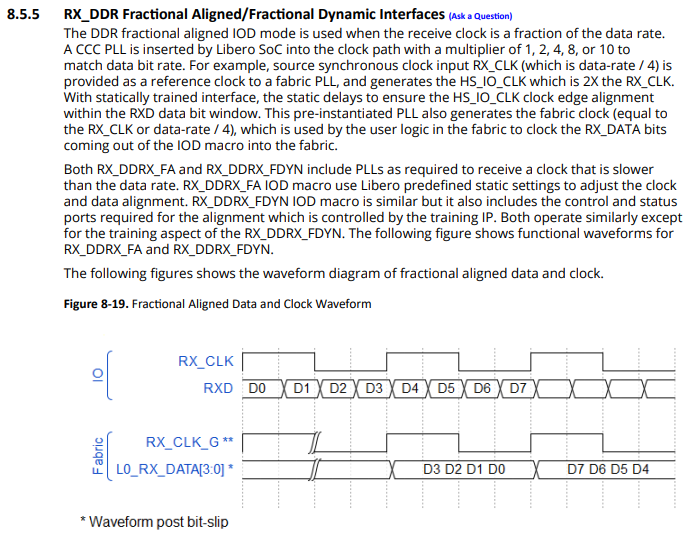

下記が「fractional aligned」なデシリアライザの正しい設定

私は「LVDSのクロックはTX_DATAと同じレートのクロックが来ている(=Aligned)」と勘違いしていたので,実態としてデシリアライザ目線で言うとデータ線が以上にバタついたデータが来ている状況になっていました.

デシリアライザの直後,上位5bitのフラグでデータの有効性を確認し,必要なものだけをFIFOに渡してからDMAをキックするビットストリームになっています.なので,正しいデータが流れ込んでこないと延々とデータが闇に葬られていくだけでDMAの動確ができません.

というわけで「fractional aligned」なデータに対応できるようにビットストリームを修正するというところに手戻りしてきました

「fractional aligned」への対応

これがまた地味にめんどくさい…

「aligned」なLVDSデータを受けるとき,ピンアサインはかなり自由に設定できます.縛りはあるにはありますが,

- Interface uses two ICB_CLKDIVDELAY and three HS_IO_CLK.

- RX_CLK input must be placed in an I/O with the CLKIN_z_w function in the same bank as other I/Os.

- RX and RX_CLK I/Os must be placed in the same bank (exception on device with bank7, I/Os can be either in both bank0 and bank7).

- One IOD per data I/Os.

- One IOA per data and clock I/Os.

- IOA from two different interfaces (TX/RX/DDR/QDR/OCTAL/CDR) cannot be placed in the same I/O lane.

ポイントはハイライトした部分.ADCからクロックを受けるピンはちょっと特殊なピンじゃないといけないです.(ぶっちゃけとはいえかなり制約は緩い)

これに対して,「fractional aligned」なLVDSデータを受ける時のピン制約はこれ

- RX_CLK input must be placed in an I/O with the CCC_CLKIN_z_w function in the same bank as other I/Os. This pin allows connection to the PLL reference clock. For more information about the available pins for each device, see PolarFire Family Clocking Resources User Guide. Other preferred clock pins are not suited for this connection.

- RX and RX_CLK I/Os must be placed in the same bank (exception on device with bank7, I/Os can be either in both bank0 and bank7).

- Interface uses a PLL to generate high-speed clock.

- One IOD per data I/Os.

- One IOA per data and clock I/Os.

- IOA from two different interfaces (TX/RX/DDR/QDR/OCTAL/IO_CDR) cannot be placed in the same I/O lane.

違うのはほぼ一点,さっきの制約が「CLKIN」ピン縛りだったのが,「CCC_CLKIN」ピンになるというのが異なります.

「全然変わんねえじゃん」と思う方いらっしゃるかもしれませんが,CCC_CLKINピンはかなり数が少ないです.簡単に言うと,polarfire SoC シリーズではパッケージの4つ角に各2個ずつ,計8個のPLLが配置されていて,そこに直接つながることのできるピンしかクロックを受けることはできません.と言っています.1からボードをフルスクラッチする場合は余っているピン全てからクロックに入力できるピンを優先的に選択してから他で辻褄を合わせに行けますが,市販ボードで動確している現在ではそもそもヘッダに出ているピンから該当するものを探し,それをベースにブレイクアウトボードの設計を検討する必要があります.

CCC_CLKINピンの罠

しかも,上記のIOユーザーガイドには書かれていない制約がどうにもありそうです.というのも,ここ3週間くらい一番躓いていたのがここなのですが,ピン配をやり直さなければならなくなった時,一番最初に検討したピン配がなぜか設定できず,そこで完全に行き詰ってしまいました.結論から言うと,そこのピンは諦めて,別のCCC_CLKINピンを使う事でブレイクアウトボードに出せるピン配を実現できたので,この問題は(一応)解決済です.

原因ですが,データシートなり読み漁った時一瞬それっぽい情報をひっかけたつもりが見失ってしまいました…

(※以下正しくないかもしれない情報なので,あくまでも参考程度にご覧ください.)

今回,取り合えずクロック入力ピンとしてbank1のCCC_CLKIN_SE_S_8というピンを使おうとしたら弾かれました.代わりに同じくbank1のCCC_CLKIN_SW_S_0というのに切り替えて,それに合わせてピン配を決めていきました.

デフォルトのビットストリームの状態で,NW(north west)のPLLをほぼ確定で使わなければならない(※FICとか使うのにNWのPLLからしかクロック入力できない都合)のですが,それに対してSE(south east)という対角のPLLを使おうとしている兼ね合いで何か制約があったのかなと推測しています.

見つけた資料(うろ覚えなので注意)では特定のpolarfire SoCチップではCCC_CLKINの一部ピンが利用できないというような話だった気がしているので,それに引っかかったのかなと思っています.

資料見つけた人いたら教えてください.お願い致します.

ブレイクアウトボード基板修正

というわけでピン配が変更になっちゃったので,それに合わせて基板も変更になります.

不幸中の幸い?だったのが,上記のCCC_CLKINピンの兼ね合いでめちゃくちゃピン配検討しまくった結果,なぜか前よりスペース的にいい感じに収まる感じになったので,一部の余ったピンを後から使えるように引き出しておきました.

あと,以前のボードから既にステッピングモータを動かせるように配線はしていたのですが,ユーロブロックに引き出していた都合で使用予定のステッピングモータからコネクタを外さないと動確できないのが嫌でそちらは一切確認してませんでした.(嫌だったというのと,あとはADCからデータ取れるようにならないとモータ回しても意味がないので後回しにしてた)

既に使う予定のモータ決まってるので,ついているコネクタを探して,そのコネクタのレセプタクルを付けられるようにしました.テストする時楽なのもそうですが,一番はスペースが圧倒的に節約できたので,これのおかげで余ったピンを引き出す余裕ができた感じです.

それにしても465円(送料込み)は安すぎるって…

終わりに

基板が届くのは来週末,バレンタインデー近辺になるという事で,物理的に進捗が途絶えたので一旦記事にしてしまいました.次こそ画が見えた報告がここで出来るとよいのですが…

ではまた.

おまけ

X(旧Twitter)で悩んでた頃の呟きをここに置いておくことにしました.

コメント